The Problem

Current hardware implementations of Ising machines are constrained to relatively small problem sizes due to scaling challenges.

Current hardware implementations of Ising machines are constrained to relatively small problem sizes due to scaling challenges.

An integrated probabilistic computer that combines a custom-designed silicon chip with the voltage-controlled magnetic tunnel junctions.

Ising machines demonstrate significant potential to tackle computationally complex challenges, including combinatorial optimization problems related to logistics, manufacturing, finance, and AI.

Professor Pedram Khalili, PhD students Jordan Athas and Christian Duffee, Yixin Shao (PhD '23)

The Ising model in physics describes how electron spins interact and arrange themselves inside a magnetic material.

Ising machines, derived from the model, are one example of the emerging field of physics-inspired computing systems that replicate physical phenomena to increase the speed and improve the energy efficiency of certain computations.

Built using electronic, magnetic, photonic, or other platforms, hardware and software implementations of Ising machines demonstrate significant potential to tackle domain-specific, computationally complex challenges. Applications range from reducing fuel costs and emissions by streamlining delivery route logistics, to optimizing production schedules in a factory, to high-speed trading in a volatile securities market.

While many tasks can be represented as combinatorial optimization problems, current implementations of Ising machines are constrained to relatively small problem sizes, due to the scaling challenges inherent to each physical platform.

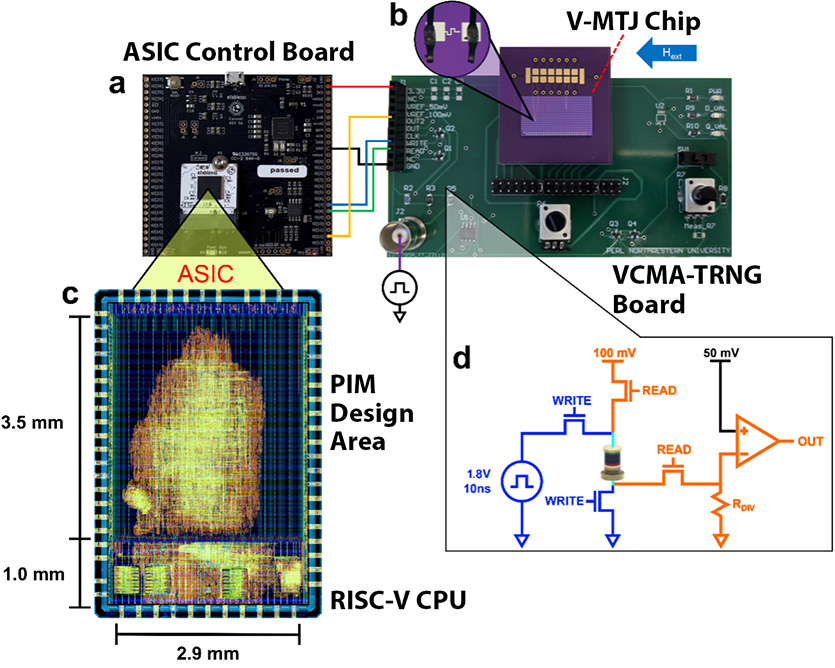

A Northwestern Engineering team led by Pedram Khalili has demonstrated a scalable approach to building a specific type of Ising machine, called a probabilistic Ising machine (PIM), or probabilistic computer. The researchers developed an integrated probabilistic computer that combines a custom-designed digital silicon chip with nanodevices based on the voltage-controlled magnetic tunnel junctions (V-MTJs) pioneered by Khalili’s Physical Electronics Research Laboratory.

The team reported their findings in the paper “An Integrated-Circuit-Based Probabilistic Computer That Uses Voltage-Controlled Magnetic Tunnel Junctions as Its Entropy Source,” published today in the journal Nature Electronics.

Electrical engineering PhD students Jordan Athas and Christian Duffee were co-first authors of the study. Collaborators also included electrical engineering alum Yixin Shao (PhD '23), Kerem Camsari (University of California, Santa Barbara), Noraica Davila Melendez and Jordan Katine (Western Digital Corporation), Giovanni Finocchio (University of Messina), and Eleonora Raimondo (University of Messina and National Institute of Geophysics and Volcanology).

PIMs consist of a network of probabilistic bits (p-bits). The two states of each p-bit element probabilistically switch back and forth between its 0 and 1. A computational problem can be mapped onto the interconnections between p-bits so that, over time, they will collectively search for and find the energy minimum — the most stable configuration of the network. If the network is designed properly, this energy minimum then corresponds to the solution of the computational problem.

“By proposing a scalable path for the implementation of PIMs using digital transistor-based technology and further enhancing it by the physics of magnetic devices, we believe that this work brings PIMs much closer to adoption for real-world computing problems,” said Khalili, AT&T Research Professor and professor of electrical and computer engineering at the McCormick School of Engineering. “This can impact many industries and applications where hard optimization problems are frequently encountered.”

Importantly, unlike some other emerging approaches to computing, Khalili explained that these PIMs can be manufactured using transistor-based technology that is commercially available today, and they operate at room temperature.

Athas and Duffee developed the 130nm application-specific integrated circuit (ASIC), which was fabricated in a complementary metal-oxide silicon (CMOS) technology available from a semiconductor foundry.

Inherent randomness, or entropy, is required for a PIM to search through its solution space, so the team also designed a true random number generator using V-MTJs addressed with an access printed circuit board.

“We leverage the intrinsic randomness of magnetic tunnel junctions, combined with clever circuit design, to inject high-quality randomness into our probabilistic computing hardware,” Athas said. “Unlike pseudorandom number generators, our MTJ-based design delivers real entropy at the hardware level, which is essential for the exploration of the Ising machine’s energy landscape.”

“We leverage the intrinsic randomness of magnetic tunnel junctions, combined with clever circuit design, to inject high-quality randomness into our probabilistic computing hardware,” Athas said. “Unlike pseudorandom number generators, our MTJ-based design delivers real entropy at the hardware level, which is essential for the exploration of the Ising machine’s energy landscape.”

MTJ-based random number generators are significantly smaller and more energy-efficient than transistor-based ones, Khalili explained.

“An MTJ-based entropy source can therefore deliver similar or higher-quality entropy to the probabilistic computer using only a few transistors, where a conventional approach would require using thousands of transistors that take up a lot of chip area,” Khalili said.

“The use of MTJs with voltage-controlled magnetic anisotropy-based random number generation enables better scalability due to an intrinsic compensation of device-to-device variation, while keeping the area occupancy smaller than full CMOS random number generation,” said Finocchio, a professor of electrical engineering at the University of Messina, Italy.

As a representative hard optimization problem, the team tested the capability of the ASIC and voltage-controlled MTJ system with integer factorization problems. They also made estimates based on simulated designs in more advanced CMOS nodes with higher transistor density that show how some large-scale problems can be mapped on future generations of the chip.

“The infrastructure exists to scale these designs to very interesting, large-scale problems. The next step is to identify these problems, and codesign probabilistic algorithms and hardware to tackle them” said Duffee.

“The infrastructure exists to scale these designs to very interesting, large-scale problems. The next step is to identify these problems, and codesign probabilistic algorithms and hardware to tackle them” said Duffee.

“Probabilistic computers are being explored today using many different strategies,” said Çamsarı, an associate professor of electrical and computer engineering at the University of California, Santa Barbara. “In this work, the team achieved two exciting milestones: first, we showed that using voltage to control magnetism can produce highly efficient probabilistic bits. Second, we demonstrated that a carefully synchronized architecture —where all bits update together like dancers moving in lockstep — can match the performance of conventional designs where each bit updates independently and unpredictably.”

Building on this initial demonstration, the research team is working on an improved design using a process technology with higher transistor density, enabling the computation of larger problems. They are also working on algorithmic improvements and designs targeting problems other than factorization, which may have more real-world commercial importance.